Jako Koło Naukowe Politechniki Warszawskiej zajmujemy się kompleksowym projektowaniem i wykonywaniem urządzeń pomiarowych i elektronicznych: od projektu koncepcyjnego, poprzez schemat elektryczny, projekt płytki drukowanej PCB, projekt obudowy, oprogramowanie (firmware i software) do uruchomienia finalnego oraz testowania urządzenia. Zapraszamy do pracowni PERG, Wydział EiTI, pok. 603B oraz 230.

9. Dodatki

9. Dodatki

9.1. Dodatek A:

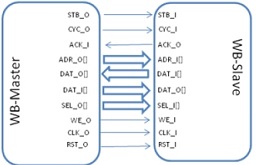

Wishbone System-on-Chip InterConnection Przez Wishbone rozumiana jest metodologia połączeń pomiędzy modułami sprzętowymi (pomiędzy tzw. IP-CORE’ami). Polega ona na wspólnym interfejsie pomiędzy nimi. Moduły kompatybilne z interfejsem są dzielone na dwa typy widoczne na rysunku 9.1:

-

Wishbone-Master (WB-Master) — jest to moduł który inicjuje transakcje (steruje innymi modułami),

-

Wishbone-Slave (WB-Slave) -– jest to moduł odpowiadający na transakcje (moduł wykonawczy).

Rysunek 9.1. Wishbone-Master i Wishbone-Slave [5]

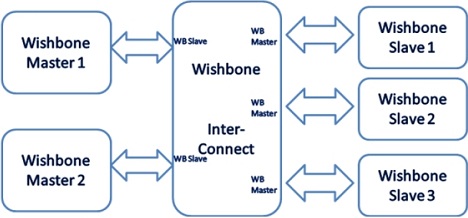

Interfejs ten nie definiuje magistrali ale tylko protokół komunikacyjny pomiędzy modułami. Magistrala tworzona jest typowo jako moduł pośredni pomiędzy modułami typu WB-Master a WB-Slave który pełni role dekodera adresu. Moduł taki typowo nazwany jest Wishbone-InterConnect, który został pokazany na rysunku 9.2.

Rysunek 9.2. Wishbone Interconnect [5]

9.1.1. Sygnały i transakcja

Zestaw sygnałów niezbędnych do przeprowadzenia komunikacji Wishbone został przedstawiony i krótko omówiony poniżej:

-

STB – (z ang. strobe) oznacza rozpoczęcie transakcji przez WB-Master,

-

CYC – (z ang. cycle) oznacza rozpoczęcie cyklu jednej lub kilku transakcji,

-

ACK – (z ang. acknowledge) wystawiany przez WB-Slave jako koniec pojedynczej transakcji,

-

ADR – (z ang. adress) linie adresowe,

-

DAT – (z ang. data) linie danych wejściowych lub wyjściowych (w niektórych urządzeniach jest to jeden zestaw linii dwu-kierunkowych),

-

SEL – (z ang. select) pokazuje na które bajty danych sąważne,

-

WE – (z ang. write enable) w stanie 1 oznacza zapis a 0 odczyt,

-

CLK – (z ang. clock) zegar taktujący moduł,

-

RST – (z ang. reset) reset modułu (zwykle synchroniczny).

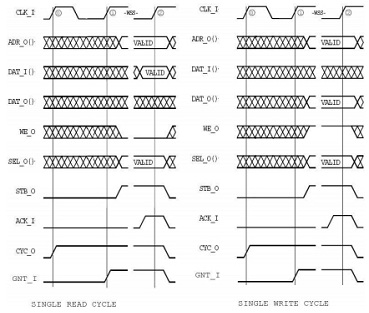

Na rysunku 9.3 przedstawiono operacje odczytu (po lewej) i zapisu (po prawej):

Rysunek 9.3. Transakcje Wishbone [37]

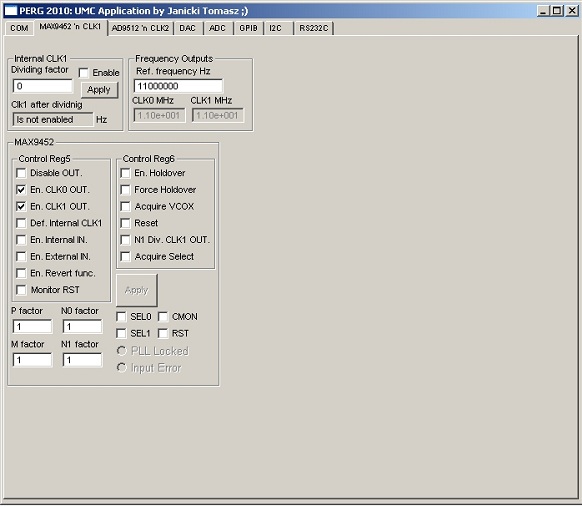

9.2. Dodatek B : Opis zakładki "MAX9452 ’n CLK1"

Rysunek 9.4. Zakładka MAX9452 ’n CLK1

Konfiguracja układu MAX9452 oraz została podzielona na 4 części:

-

Grupa Control Reg5

Disable OUT.

Ustawienie powoduje, iż wyjsćia układu sąwprowadzane w stan niskiEn. CLK0 OUT.

Ustawienie powoduje, iż wyjsćie CLK0 układu jest włączane - unieważnia to ustawienie "Disable OUT."En. CLK1 OUT.

Ustawienie powoduje, iż wyjsćie CLK1 układu jest włączane - unieważnia to ustawienie "Disable OUT."En. Def. CLK1.

Ustawienie powoduje, iż zegar wewnętrzny zostanie wybrany domyślnie1 jako referencyjny. W przeciwnym razie będzie to zegar zewnętrzny.En. Internal IN.

Ustawienie powoduje włączenie wejsćia wewnętrznego zegaraEn. External IN.

Ustawienie powoduje włączenie wejsćia zewnętrznego zegaraEn. Revert. func.

Ustawienie powoduje włączenie funkcji automatycznego wybierania domyslego zegara w przypadku wyjścia układu ze stanu "Input Error"Monitor RST

Ustawienie resetuje monitor wejść układu - wymagane przy wymuszeniu wyjścia układu ze stanu "Input Error"

-

Grupa Control Reg6

En. Holdover

Ustawienie włącza funkcję Holdover, dzięki której układ ustala częstotliwość nominalnąw momencie pojawienia się błędu na obu wejsćiachForce Holdover

Ustawienie powoduje wymuszenie uruchomienia funkcji HoldoverAcquire VCOX

Ustawienie powoduje zapamiętanie częstotliwości nominalnejReset

Ustawienie powoduje, że użytkownik wprowadza układ w stan resetu.N1 Div. CLK1 OUT.

Ustawienie powoduje, iż współczynniki N0 oraz N2 konfigurują niezależnie kolejno CLK0 i CLK1. W przypadku nie ustawienia, oba wyjścia konfigurowane są przez N0.Acquire Select

Ustawienie powoduje, iż częstotliwość jest ustalana przy wykorzystaniu zapamiętanej nominalne częstotliwości. W przypadku nie ustawienia częstotliwość kontrolowana jest poprzez wewnętrzną pętlę PLL.

-

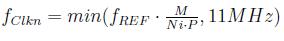

Ustalanie częstotliwości wyjściowej

Ustalanie częstotliwości polega na wpisaniu odpowiednich wartości w pola N, P i M zgodnie z poniższym wzorem:

-

Częstotliwość maksymalna 11MHz jest spowodowana tym, iż do układu podłączony jest oscylator o częstotliwosći 11MHz. Istnieje możliwość podłączenia oscylatora o wyższej częstotliwości (do 160MHz), wówczas należy uwzględnić tę poprawkę we wzorze.

-

Interfejs równoległy

Użytkownik steruje liniami SEL0, SEL1, CMON oraz RST poprzez kontrolki o tych samych nazwach co linie. Poprzez ustawienie SEL0 i SEL1, gdy kontrolki "En. Internal IN." i "En. External In." nie są ustawione, to użytkownik konfiguruje jakie wejsćia zegarowe mają zostać włączone. Liną tym odpowiadają zegar zewnętrzny (SEL0) i zegar wewnętrzny (SEL1).Poprzez ustawienie linii RST użytkownik wprowadza układ w stan resetu. Poprzez ustawienie linii CMON użytkownik włącza tryb monitorowania wejść układu. Niezbędne do ustawienia, gdy chcemy uzyskać informację o błędzie wejść "Input

Error". Gdy pojawia się błąd "Input Error", to na wyjsćiach układu pojawia się sygnał 11MHz.

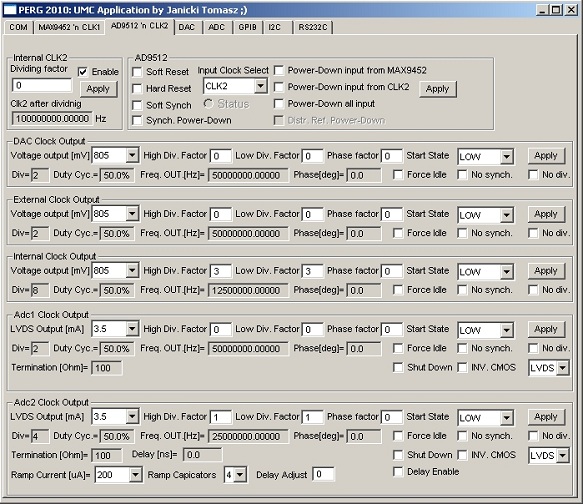

9.3. Dodatek C : Opis zakładki "AD9512 ’n CLK2"

Rysunek 9.5. Zakładka AD9512 ’n CLK2

Konfiguracja układu AD9512 została podzielona na 2 główne części:

-

Grupa AD9512

Soft Reset

Ustawienie powoduje programowy reset układu AD9512, wszystkie rejestry poza rejstrem z wewnętrznego adresu 0x00h układu,Hard Reset

Ustawienie powoduje sprzętowy reset układu AD9512, który różni się od programowego tym, że wszystkie rejestry układu sąwprowadzane w znany stan,Soft Synch

Ustawienie powoduje wprowadzenie wyjść układu AD9512 w stan synchronizmu tj. wyrównania faz,Synch. Power-Down

Ustawienie odłącza sekcję synchronizacji wyjść układu AD9512,Power-Down input from MAX9452

Ustawienie odłącza sekcję wejsćia do którego podłączone jest wyjsćie układu MAX9452,Power-Down input from CLK2

Ustawienie odłącza sekcję wejsćia do którego podłączony jest CLK2 (wewnętrzny zegar z układu FPGA),Power-Down all input

Ustawienie odłącza sekcję wejść sygnałów zegarowych układu AD9512,Distr. Ref Power-Down

Ustawienie nie jest dostępne ze względu na możliwość uszkodzenia układu (por. [32] str. 31),Input Clock Select

Ustawia jaki zegar jest wprowadzany na układy przetworników:- ustawienie "CLK2", pochodzący z układu FPGA,

- ustawienie "MAX9452", pochodzący z wyjsćia układu MAX9452.

-

Grupa Clock Output

Poszczególne okna konfigurują zegary poszczególnych wyjść układu AD9512:

- "DAC Clock Output" zmienia ustawienia zegara wchodzącego na układ AD9777 (DAC),

- "Interal Clock Output" zmienia ustawienia zegara wchodzącego z powrotem do układu FPGA, który można następnie wykorzystać do dowolnych celów,

- "External Clock Output" zmienia ustawienia zegara wychodzącego na zewnętrzne złącze CON9,

- "ADC1 Clock Output zmienia ustawienia zegara wchodzącego na układ LTC2207 (ADC1), czyli pierwszego przetwornika analogowo-cyfrowego,

- "ADC2 Clock Output zmienia ustawienia zegara wchodzącego na układ LTC2207 (ADC2), czyli drugiego przetwornika analogowo-cyfrowego.

Ustawieniami wspólnymi dla wszystkich okien "Clock Output" są:

-

Ustawienie dzielników częstotliwości albo ich brak,

-

Ustawienie przesuwnika fazy,

-

Ustawienie odpowiednich poziomów napięć albo prądów wyjść zegarowych,

-

Ustawienie ignorowania stanu linii FUNCTION dla poszczególnych wyjść (w przypadku skonfigurowania linii FUNCTION jak funkcję SYNCB),

-

Odłączenie danego wyjsćia – ustawienie "force idle" wraz z "No synch.",

-

Możliwość ustawienia stanu początkowego sygnałów zegarowych wyjść – stan niski albo stan wysoki.

Ustawieniami dodatkowym dla zegarów wychodzących na układy ADC są:

-

Ustawienie standardu wyjść – LVDS albo CMOS,

-

Bezpośrednie (i zarazem dodatkowe) wyłączenie wyjść,

-

Ustawienie "odwróconego" sygnału CMOS, w przypadku wybrania standardu wyjść CMOS.

Ustawieniami dodatkowymi tylko dla sygnału zegarowego wychodzącego na drugi układ ADC (ADC2) są ustawienia opózńienia, realizowane dzięki ustawieniom "Ramp Capicators", "Delay Adjust" oraz "Ramp Current". Ustawione opóźnienie wyświetlane jest oknie "Delay [ns]". Ustawianie opóźnienia jest możliwe tylko jeśli zostało ustawione "Delay Enable".

Wszystkie wyżej wymienione ustawienia są wprowadzane do układu AD9512 poprzez naciśnięcie przycisku "Apply" w poszczególnych grupach ustawień.

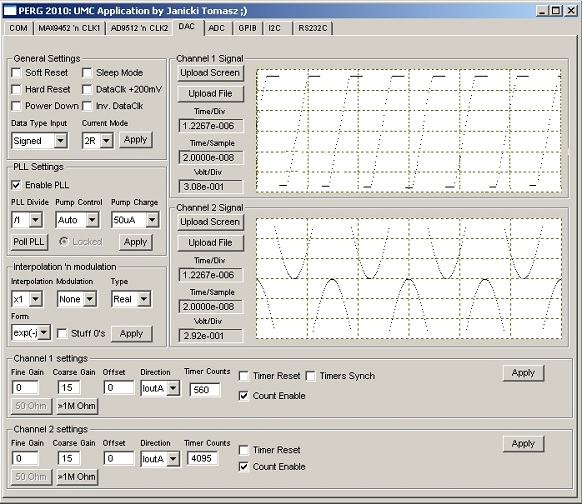

9.4. Dodatek D : Opis zakładki "DAC"

Rysunek 9.6. Zakładka DAC

Konfiguracja układu AD9777 została podzielona na 5 głównych części:

-

Grupa General Settings

Soft Reset

Ustawienie powoduje programowy reset układu AD9777, powodujący wprowadzenie wszystkich rejestrów konfiguracyjnych w znany stan, poza rejestrem spod wewnętrznego adresu 0x00h układu AD9777,Hard Reset

Ustawienie powoduje programowy reset układu AD9777, powodujący wprowadzenie wszystkich rejestrów konfiguracyjnych w znany stan,Power Down

Ustawienie powoduje odłączenie częsći analogowych i cyfrowych układu AD9777, poza częsćią odpowiedzialną za komunikację po SPI,Sleep Mode

Ustawienie powoduje odłączenie wyjść układu AD9777,Data Clk +200mV

Ustawienie zwiększa wydajność prądową wyjsćia zegarowego DATACLK z układu AD9777, co zwiększa amplitudę sygnału o około 200mV,Inv. DataClk

Ustawienie odwraca sygnał zegarowy na wyjściu DATACLK,Data Type Input

Ustawienie interpretacji danych wejściowych:

- U2,

- binarnie bez znaku.Current Mode

Ustawienie prądu referencyjnego IRef :

- R ustawia ok 1.2mA, które jest rozdzielane na dwa kanały po połowie,

- 2R ustawia dla kanału pierwszego ok 1.2mA, a dla drugiego ok 0.6mA.

-

Grupa PLL Settings

Enable PLL

Ustawienie włącza pętlę PLL,PLL Divide

Ustawienie podzielnika pętli PLL,Pump Control

Ustawienie kontroli prądowej pętli PLL:

- Auto – prąd jest dostosowywany automatycznie,

- Manual – prąd jest ustawioany przez użytkownika w polu "Pump Charge".

-

Grupa Interpolation ’n modulation

Interpolation

Ustawienie mnożnika interpolacji: 1x, 2x, 4x, 8x, gdzie 1x oznacza brak interpolacji,Modulation

Ustawienie podzielnika modulacji: brak, /2, /4, /8,Type

Ustawienie typu modulacji: rzeczywista albo zespolona,Form

Ustawienie modulacji za pomocą funkcji: exp(−j!t), exp(+j!t)Stuff 0’s

Ustawienie powodujące "wstawianie zer", w przypadku interpolacji i modulacji, powodujcie poprawienie odpowiedzi częstotliwościowej układu (por. [31] str. 38).

-

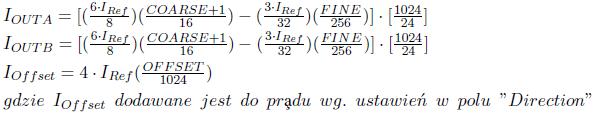

Grupy Channel Settings

Fine Gain, Coarse Gain, Offset, Direction

Ustawienie maksymalnych prądów wyjsćiowych wg. wzoru podanego poniżej:Timer Counts

Ustawienie wartości modulo liczników adresu,Reset

Ustawienie powoduje zresetowanie licznika adresu,Count Enable

Ustawienie powoduje start inkrementacji licznika, pod warunkiem nie ustawianego resetu i nie ustawionego pola "Timers Synch",Timers Synch

Ustawienie powoduje zresetowanie liczników adresu dla obu kanałów, dzięki czemu możliwe jest uzyskanie synchronizacji wytwarzanych sygnałów,50Ohm, 1MOhm

Ustawienie powodujące zmianę jedynie w obliczaniu pola "Volt/Div". Dla ustawienia 50Ohm wartość jest odpowiednio mniejsza, tak jakby rezystancja wejściowa woltomierza, który mierzymy wartości napięć wytwarzanego sygnału, miała wartość 50.

-

Grupy Channel Signal

Upload Screen

Wciśnięcie powoduje wgranie do przetwornika sygnału widocznego na przebiegu. Próbki sygnału wgrane w ten sposób są wynikiem odpowiedniej liniowej aproksymacji wartości pozycji pikseli. Jest to spowodowane tym, iż rozdzielczość okienka podglądu sygnału jest mniejsza zarówno od rozdzielczosći przetwornika jak i pojemności pamięci (przypisanej kanałów przetwornika DAC),Upload File

Wciśniecie powoduje wgranie do przetwornika sygnału określonego numerycznie w pliku. Możliwe są 3 formaty:

Binarnie

Format : [8bit][8bit]...[8bit][8bit]

– słowa 16-bitowe zapisane na kolejnych parach 8-bitowych, gdzie starszy bajt zapisywany jest jako pierwszy od lewej,Liczby całkowite ze znakiem

Format : [int], [int], ..., [int]

– przecinki oddzielają liczby, bez spacji,Przykład: 12,−34, 100, 85

Liczby zmienno-przecinkowe

Format : [float], [float], ..., [float]

– przecinki oddzielają liczby, bez spacji.Przykład: 0.1,−0.3, 1.04 lub 1e − 001,−3e − 001, 1.04e − 000

9.5. Dodatek E : Składnia języka skryptowego zakładki GPIB

Składnia języka składa się z funkcji, gdzie każda winna być zakończona znakiem średnika (poza instrukcjami pętli "while" i skoku "if"). Zaimplementowano obliczanie prostych wyrażeń matematycznych i tworzenie zmiennych, co pozwala na tworzenie bardziej złożonych procedur pomiarowych. Została dodana również możliwość komentowania pojedynczej linii kodu przy pomocy znaku "#".

Pełne przykłady wykorzystania języka zostały przedstawione w przykładach znajdujących się w plikach (o rozszerzeniu .gpib) w katalogu "testGpib"

Przy obliczaniu wyrażeń dostępne są operatory i funkcje (przedstawione w kolejności pierwszeństwa wykonywania):

-

checksrq() – funkcja sprawdza aktualny stan linii SRQ.

Jeśli stan jest aktywny, to zwracana jest wartość 0xffh, w przeciwnym wypadku 0x00h.

Funkcja ta musi występować sama (bez innych operatorów i funkcji) w pojedynczym wyrażeniu,Przykład : $Wzmienna=checksrq();

Przykład : if( checksrq() ) {$Wzmienna2 = 34;}

-

readbyte() – funkcja odczytuje pojedynczy bajt z kolejki wyjściowej kontrolera GPIB i zwraca jego wartość.

Jeśli kolejka wyjsćiowa jest pusta zwracaną wartosćią jest -1. Funkcja ta musi występować sama (bez innych operatorów i funkcji) w pojedynczym wyrażeniu,Przykład : $Wzmienna=readbyte();

-

Operatory:

- mnożenie i dzielenie: "*", "/",

- dodawanie i odejmowanie: "+", "-",

- operacje na bitach AND oraz OR: "&", "|",

- operacje porównywania, gdzie zwracanąwartosćią porównania jest 1 albo 0: ">", ">=", "==", "<=", "<", !=,

- operacje logiczne AND oraz OR, gdzie zwracaną wartosćią operacji logicznych jest 1 albo 0: "&&", "||".Przykład : $zmienna= ((12 + 4) | 34 ) <= 0;

-

Ponadto:

- Zwarzywszy na wykorzystany algorytm iteracyjny obliczania wyrazów dostępna jest nieograniczona ilość poziomów nawiasów "(", "),

- Wartości obliczanych wyrażeń i zmiennych są typu całkowitego,

- Deklarowanie zmiennych odbywa się przy wpisaniu nazwy zmiennej poprzedzonej znakiem "$",

- Nazwa zmiennej powinna zawierać małe litery, poza pierwszą opcjonalną literą (wielką) "W", która ustawia flagę "watch" dla danej zmiennej. Ustawienie tej flagi pozwala na podglądanie wartosći zmiennej w oknie, po wcisńięciu "Enable". Zmienna i jej nowa wartość wyświetlane są za każdym razem, gdy zmienna zmienia wartość.Przykład : $Wzmienna= 23 + (22 > 3);

– spowoduje wyświetlenie w oknie podglądu zmienna=24

Do sterownia interfejsem GPIB zostały zaimplementowane następujące funkcje:

-

runifc() – funkcja wprowadza linię ATN w stan aktywny na czas określony przez moduł sprzętowy kontrolera GPIB,

-

sendtext(string, expression) – funkcja wysyła tekst (string) programujący do urządzeń docelowych. Przez wyrażenie (expression) użytkownik określa czy wraz z ostatnim znakiem linia EOI ma być wprowadzona w stan aktywny, pod warunkiem że wyrażenie jest logicznie prawdziwe,

Przykład : $sendtext("text\"cytat\" drugi text", 1);

-

sendcommand(string, expression) – funkcja wysyła komendy (string) uniwersalne do urządzeń docelowych. Zbiór zaimplementowanych komend: GTL, SDC, PPC, GET, TCT, LLO, DCL, PPU, SPE,SPD, LAD, UNL, TAD, UNT.

W przypadku komend TAD i LAD wyrażeniem (expresion) jest adres urządzenia (z zakresu od 0 do 30),Przykład : sendcommand("TAD", 3);

-

setatn(expression) – funkcja ustawia linę ATN w odpowiedni stan w zależności od wyrażenia. Jeśli wyrażenie jest prawdziwe, to ATN wprowadzane jest w stan aktywny. Jeśli wyrażenie jest nieprawdziwe, to ATN staje się nieaktywne,

-

openfile(string, expression) – funkcja w zależności od wyrażenia (expression) tworzy lub otwiera plik o ścieżce dostępu string. Plik ten jest dalej wykorzystywany przy wykonywaniu funkcji "getdata" i "setdata". W wyrażeniu użytkownik precyzuje:

- otwarcie pliku do odczytu, gdy wyrażenie jest mniejsze lub równe 0,

- stworzenie pliku do zapisu, gdy wyrażenie jest równe 1,

- otwarcie pliku do zapisu na końcu tego pliku, gdy wyrażenie jest większe niż 1.Przykład : openfile("moj_plik.txt", 0);

-

getdata(expression) – funkcja odbiera dane przesłane z urządzeń pomiarowych i wpisuje je do pliku otwartego za pomocą funkcji "openfile". W wyrażeniu (expression) użytkownik precyzuje:

- gdy wyrażenie jest większe od 0, to wyrażenie określa ile bajtów należy odczytać,

- gdy wyrażenie jest równe 0, to odczyt ma trwać dopóki nie zostanie napotkany terminator (LF),

- gdy wyrażenie jest mniejsze od 0, to odczyt ma trwać dopóki nie nastąpi limit czasu odpowiedzi.Typowo przez ustawienie wyrażenia na mniej niż 0, z urządzenia docelowego jest odbierana cała przewidywana transmisja.

Przykład : getdata(-1);

-

setdata(expression, expression, expression) – funkcja nadaje dane zapisane w pliku, otwartego za pomocą "openfile", do urządzeń docelowych. W kolejnych wyrażeniach użytkownik precyzuje:

Wyrażenie 1:

- gdy wyrażenie jest większe od 0, to wyrażenie określa ile bajtów należy nadać,

- gdy wyrażenie jest równe 0, to nadawanie ma trwać dopóki nie zostanie napotkany terminator (LF) w pliku,

- gdy wyrażenie jest mniejsze od 0, to nadawanie ma trwać dopóki nie nastąpi koniec pliku lub limit czasu na odebranie danych przez urządzenia docelowe.Wyrażenie 2:

- podaje od jakiej pozycji pliku zaczynają się dane do przesłania;

- podanie wartosći dodatniej spowoduje ustawienie pozycji względem początku pliku.

- podanie wartości ujemnej spowoduje ustawienie względem końca pliku.

- podanie wartosći 0 ustawia pozycję na początek pliku,Wyrażenie 3:

– gdy jest prawdziwe, to wraz z ostatnim przesyłanym bajtem ustawiana jest linia EOI w stan aktywny.Przykład : setdata(-1,0,1);

-

readout(expression, expression) – funkcja powoduje odebranie danych z urządzeń pomiarowych. W kolejnych wyrażeniach użytkownik precyzuje:

Wyrażenie 1:

- gdy wyrażenie jest większe od 0, to wyrażenie określa ile bajtów należy odebrać,

- gdy wyrażenie jest równe 0, to odbiór ma trwać dopóki nie zostanie napotkany terminator (LF) w pliku,

- gdy wyrażenie jest mniejsze od 0, to odbiór ma trwać dopóki nie nastąpi limit czasu odpowiedzi.Wyrażenie 2:

– gdy jest prawdziwe i został wciśnięty przycisk "Enable", to odebrane dane widoczne sąw oknie podglądu wykonywania kodu.Przykład : readout(-1,1);

-

wait(expression, expression, expression, expression, expression) – funkcja powoduje wstrzymanie wykonywania kodu na określony odstęp czasu oraz zmiany ustawień limitów czasowych.

W kolejnych wyrażeniach użytkownik precyzuje:Wyrażenie 1:

– powoduje odczekanie odstępu czasowego,Wyrażenie 2:

– powoduje zmiany ilości prób odebrania danej,Wyrażenie 3

– powoduje zmiany ilości prób nadania danej,Wyrażenie 4:

– powoduje zmiany odstępu czasowego pomiędzy próbami nadawania/odbierania i wraz z ilosćią prób stanowi limit czasowy odpowiedzi/nadawania,Wyrażenie 5:

– powoduje zmianę odstępu czasowego wykonywania funkcji "runifc".Wszystkie odstępy czasowe podawane sąw ms. Podanie ujemnej wartosći spowoduje brak zmian.

Przykład : wait(100,-1,-1,-1,-1);

-

writefile(string, expression) – funkcja powoduje wpisanie zapis ciągu znaków (string) do pliku otwartego przy pomocy funkcji "openfile". Za pomocą wyrażenia, gdy jest prawdziwe, użytkownik precyzuje że ciąg znaków zakonćzony jest konćem linii ("\n"), który róznież zostaje wpisany do pliku.

Przykład : writefile("koniec pliku", 0);