Jako Koło Naukowe Politechniki Warszawskiej zajmujemy się kompleksowym projektowaniem i wykonywaniem urządzeń pomiarowych i elektronicznych: od projektu koncepcyjnego, poprzez schemat elektryczny, projekt płytki drukowanej PCB, projekt obudowy, oprogramowanie (firmware i software) do uruchomienia finalnego oraz testowania urządzenia. Zapraszamy do pracowni PERG, Wydział EiTI, pok. 603B oraz 230.

3. Koncepcja systemu pomiarowego

3. Koncepcja systemu pomiarowego

Koncepcja systemu pomiarowego została podzielona na dwie warstwy: sprzętową (firmware) oraz programową (software). W pierwszej kolejności została opracowana koncepcja warstwy sprzętowej, przedstawiona w roz. 3.1, gdyż rzutowała na kształt koncepcji warstwy programowej, przedstawionej w roz. 3.2.

3.1. Warstwa sprzętowa

Koncepcję warstwy sprzętowej podzielono na trzy części:

-

konfigurację systemu i metodę komunikacji,

-

sposób sterowania systemem,

-

wykorzystanie i rozplanowanie zasobów FPGA.

3.1.1. Konfiguracja i metoda komunikacji

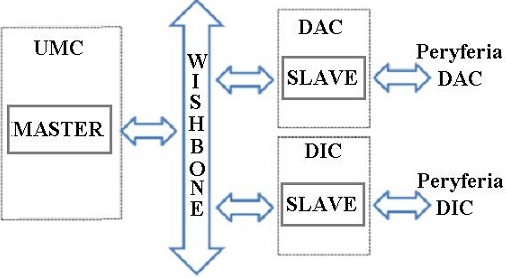

Rysunek 3.1 ideowo pokazuje konfigurację systemu oraz metodę komunikacji, które następnie zostały krótko opisane.

Rysunek 3.1. Konfiguracja systemu i sposób komunikacji [5]

Przyjęto konfiguracje systemu w formie master/slave (bez systemu przerwań). Rozwiązanie to jest proste w realizacji i wystarczające przy przetwarzaniu blokowym. Do realizacji systemu został wybrany sposób komunikacji Wishbone [37] (patrz dodatek A) z następujących powodów:

-

prostoty implementacji,

-

dostępności licznych modułów sprzętowych, wykorzystujących sposób Wishbone do komunikacji (tzw. moduły "Wishbone Compilant"), w bibliotece elementów Altium Designer 6.3 oraz na sieci internetowej (tzw. moduły open-core),

-

braku ograniczeń na częstotliwość zegara,

-

braku multipleksowanej szyny danych i adresowej.

Komunikacja Wishbone nie jest jednak rozwiązaniem standardowym. Komunikacja ta jest jednak szeroko wykorzystywana w modułach sprzętowych, zwłaszcza wśród projektantów związanych ze społecznościami open-source, dowodem tego jest powstawanie coraz większej ilości rozwiązań opartych o metodologię Wishbone, dostępnych między innymi na stronach www.opencores.org .

3.1.2. Sposób sterowania systemem

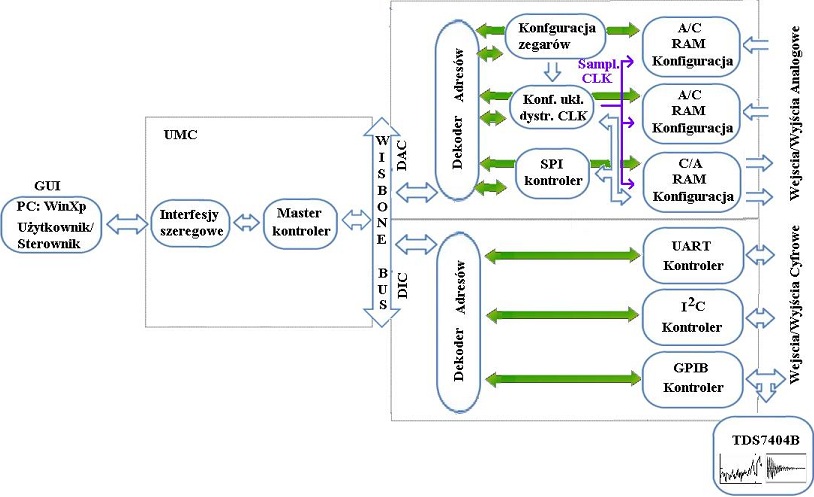

Na rysunku 3.2 pokazano ogólnie sposób sterowania systemem.

Rysunek 3.2. Sposób sterownia [5]

Ustalona z góry topologia połączeń (magistralowa) między UMC, a płytami nakładkowymi DAC i DIC, oraz fakt iż płyta UMC dysponuje licznymi cyfrowymi interfejsami wej/wyj, spowodowała wykorzystanie jej układu FPGA jako mostu systemowego. Zadaniem mostu jest odpowiednia translacja poleceń, wysyłanych z aplikacji użytkownika i wykonywanie ich na magistrali Wishbone. Do celów komunikacji GUI z UMC wykorzystano interfejsy szeregowe płyty UMC: RS232 i USB. Są one dostatecznie szybkie do celów blokowego przetwarzania danych.

3.1.3. Wykorzystanie i rozplanowanie zasobów

Rysunek 3.3 przedstawia wykorzystanie i rozplanowanie zasobów PWMSF i laboratorium PERG.

Rysunek 3.3. Wykorzystanie i rozplanowanie zasobów PWMSF i laboratorium PERG

Ustalono następujące wykorzystanie zasobów:

-

Wykorzystanie przetworników A/C i C/A, znajdujących się na płycie DAC, realizujących odpowiednią konwersję sygnałów. W celu obsłużenia przetworników, zostały im przydzielone bloki pamięci RAM układu FPGA, oraz układy konfiguracji. Do uzyskania konwersji sygnałów, zostały wykorzystane układy konfiguracji (MAX9452) i dystrybucji (AD9512) zegara próbkującego. Dodatkowo, w celach rozszerzenia możliwości konfiguracyjnych sygnałów zegarowych, zaimplementowano programowalny dzielnik.

-

Wykorzystanie interfejsu GPIB, znajdującego się na płycie DIC. Interfejs ten umożliwił komunikację z innymi urządzeniami, takimi jak dostępny w laboratorium oscyloskop TDS7404B firmy Tektronix. Pozwoliło to na przeniesienie zadania analizy sygnałów na TDS7404B, który ma możliwości analiz czasowej i widmowej.

-

Wykorzystanie interfejsu RS232C oraz I2C, znajdujących się na płycie DIC. Interfejs ten umożliwił komunikację z licznymi urządzeniami nie wymagającymi dużych szybkości transferu, takimi jak przetworniki czy mikrokontrolery Wszystkie bloki sprzętowe, na poszczególnych płytach, zostały dołączone do dekodera adresowego. Liczba dostępnych adresów określona została przez sposób komunikacji Wishbone: wykorzystano 24-bitową szynę adresową. Ostateczne przydzielenie adresów odpowiednim blokom nastąpiło podczas realizacji systemu (patrz. roz. 4).

3.2. Warstwa programowa

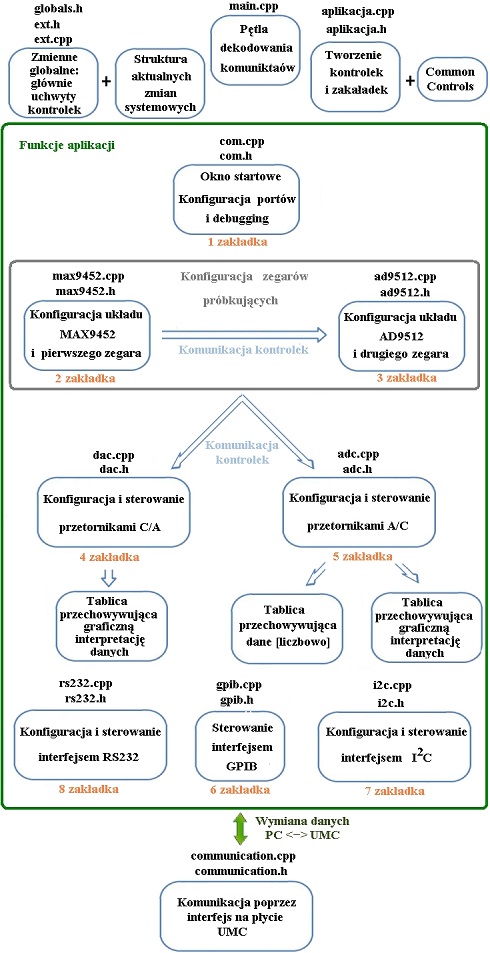

Struktura aplikacji użytkownika prezentowana jest na rysunku 3.4.

Rysunek 3.4. Struktura programu powiązana z funkcjami

Aplikacja została podzielona na odpowiednie części. Fizycznie tymi częściami są odrębne pliki źródłowe. Każdy osobny plik zawiera funkcje, które dostępne są dla użytkownika w odrębnych zakładkach po uruchomieniu aplikacji. Zakładki zostały dobrane tak by logicznie dzieliły funkcjonalności systemu. Dzięki takiemu podejściu uzyskano strukturę modularną aplikacji ułatwiającą jej tworzenie i testowanie.

Utworzono następujący podział funkcjonalności:

Zakładka 1

Użytkownik konfiguruje port szeregowy do transmisji pomiędzy PC a UMC. Dodatkowo została przewidziana implementacja funkcji debugingu, ułatwiająca opracowywanie modułów sprzętowych.

Zakładka 2

Użytkownik konfiguruje układ MAX9452 oraz pierwszy zegar podchodzący z układu FPGA. Ustawienia te mają wpływ na wartości częstotliwości ustawianych w zakładce trzeciej, czwartej oraz piątej. Niezbędne parametry przekazywane są do tych zakładek poprzez zmienne globalne i strukturę przechowującą bieżące ustawienia systemowe.

Zakładka 3

Użytkownik konfiguruje układ AD9512 oraz drugi zegar pochodzący z układu FPGA. Ustawienia te mają wpływ na częstotliwość próbkowania przy generacji oraz akwizycji sygnałów. Niezbędne parametry przekazywane są do zakładki czwartej i piątej poprzez zmienne globalne i strukturę przechowującą bieżące ustawienia systemowe.

Zakładka 4

Użytkownik konfiguruje i steruje układem AD9777. Przewidziano możliwość wstępnej (mniej dokładnej) analizy generowanego sygnału dzięki jego graficznej interpretacji w oknie podglądu sygnału. Graficzna interpretacja sygnału przechowywana jest w tablicy, której wartości odpowiadają odpowiednim koordynatom (w pikselach) na ekranie.

Zakładka 5

Użytkownik konfiguruje i steruje układami LTC2207. Przewidziano możliwość wstępnej (mniej dokładnej) analizy spróbkowanego sygnału dzięki jego graficznej interpretacji w oknie podglądu sygnału. Graficzna interpretacja sygnału przechowywana jest w tablicy, której wartości odpowiadają odpowiednim koordynatom (w pikselach) na ekranie. Dodatkowo zakładka ta korzysta z tablicy, w której zapisywane są wartości spróbkowanego sygnału. Wartości te mogą następnie zostać zapisane do pliku, co daje przenośność wykonanego pomiaru na inne oprogramowanie w celach ewentualnej dalszej analizy lub dokładniejszego podglądu.

Zakładka 6

Użytkownik steruje interfejsem GPIB pisząc odpowiedni kod sterujący napisany w zaimplementowanym języku skryptowym, dając przez to możliwość tworzenia procedur pomiarowych. Dodatkowo przewidziano możliwość podglądu odebranych danych z urządzeń docelowych.

Zakładka 7

Użytkownik steruje interfejsem I2C pisząc odpowiedni kod sterujący. Dodatkowo, przy odczytach z urządzeń, w oknie podglądu widoczne są zwracane wartości.

Zakładka 8

Użytkownik steruje interfejsem RS232C. Przewidziano dwa tryby przesyłania danych: tekstowy oraz binarny. W trybie tekstowym wpisywana jest odpowiednia treść, a w trybie binarnym wpisywana są wartości heksadecymalne każdego bajtu. Tryb przesyłania danych jednocześnie ustala tryb odbierania danych. Opis działania programu przedstawiono krokowo poniżej:

-

Program rozpoczyna się w funkcjimain(), skąd przechodzi do załadowania biblioteki "Common Controls" [38], a następnie do tworzenia okien (zakładek i kontrolek)

-

Po stworzeniu okien program przechodzi do głównej pętli dekodowania komunikatów, czekając na reakcję użytkownika. Stąd skok zachodzi do jednej z ośmiu zakładek.

-

Po zareagowaniu na reakcję użytkownika (wykonaniu wskazanej przez użytkownika funkcji) dochodzi w większości przypadków do transmisji pomiędzy UMC a PC poprzez port szeregowy. Sposób transmisji oraz programowej metody wymuszania poprawności transmisji został opisany również w oddzielnym zbiorze plików. Typowo po zakończeniu transmisji program przechodzi z powrotem do głównej pętli dekodowania komunikatów.

---------------------

-

Samer Bou Habib, Ryszard Romaniuk. Opracowanie Mostu PCI dla Węzła Modularnego Systemu Fotonicznego. Politechnika Warszawska, 2008.

-

WISHBONE System-on-chip (SoC) Interconnection Architechture for Portable IP Cores Revision B.3, Septmeber 2002.

-

Microsoft. About Common Controls. http://msdn.microsoft.com/en-us/library/bb775493(VS.85,loband).aspx, 2009.