Jako Koło Naukowe Politechniki Warszawskiej zajmujemy się kompleksowym projektowaniem i wykonywaniem urządzeń pomiarowych i elektronicznych: od projektu koncepcyjnego, poprzez schemat elektryczny, projekt płytki drukowanej PCB, projekt obudowy, oprogramowanie (firmware i software) do uruchomienia finalnego oraz testowania urządzenia. Zapraszamy do pracowni PERG, Wydział EiTI, pok. 603B oraz 230.

1. Wstęp

1. Wstęp

Urządzenia elektroniczne od wielu lat są wykorzystywane jako aparatura do wykonywania pomiarów, przy czym poziom skomplikowania tej aparatury zależy od problemu postawionego w eksperymencie oraz poziomu technologicznego jakim dysponujemy. Stąd wykorzystanie aparatury może sięgać od niedokładnego multimetru, aż do rozproszonej sieci systemów pomiarowych, składających się urządzeń najwyższej klasy, wykonujących ogromne ilości zautomatyzowanych oraz zsynchronizowanych pomiarów.

W niniejszej pracy został opisany proces budowania aparatury pomiarowej, obsługiwanej komputerowo, służącej do mierzenia i wytwarzania przebiegów sygnału napięciowego. Proces ten obejmuje wykorzystanie zarówno nietrywialnych narzędzi projektowych dostępnych na dzisiejszym rynku jak i również wykorzystanie rozwiązań sprzętowych i programistycznych typu open-source. Tak przygotowane środowisko projektanta umożliwiło integrację dostępnych jednostek funkcjonalnych w pełny system pomiarowy.

1.1. Systemy rozproszone

Systemy Rozproszone (z ang. distributed systems) są to systemy składające się z wielu samodzielnych jednostek funkcjonalnych, połączonych w jedną całość przy pomocy sieci komunikacyjnej i rozproszonego oprogramowania. Trzema wyróżniającymi cechami takich systemów są:

-

Przezroczystość – system nie jest obsługiwany przez użytkownika jako zbiór pojedynczych jednostek lecz jako jednolita całość,

-

Skalowalność/Odwracalność – do zaprojektowanego systemu można w łatwy sposób dołączać/odłączać jednostki funkcjonalne,

-

Współbieżność – system jest zdolny do wykonywania wielu zadań w tym samym czasie.

Pewną klasę takich systemów tworzą Rozproszone Systemy Pomiarowe (RSP [1]). Elementy takiego systemu (węzły) rozmieszczane są terytorialnie i są ze sobą połączone przewodami (sieci komputerowe, przemysłowe etc.) lub bezprzewodowo (podczerwień, radio, Bluetooth [2]). Jednostkami systemu są typowo urządzenia pomiarowe (jednostki wykonawcze) i sterujące (kontrolery). RSP mogą być sklasyfikowane według stopnia zapotrzebowania na obsługę:

-

Wymagana sporadyczna kontrola i sporadyczne sterowanie. W takich systemach jednostki funkcjonalne są zdolne do podejmowania większości decyzji niezależnie, a wyniki ich pomiarów są odczytywane okresowo. Takimi systemami mogą być stacje meteorologiczne, których pomiary są odczytywane jedynie okresowo ze względu na względnie powolny charakter zmian warunków pogodowych.

-

Wymagana ciągła kontrola i sporadyczne sterowanie. W takich systemach, podobnie jak powyżej, jednostki podejmują w większość decyzji niezależnie, ale wyniki ich pomiarów są odczytywane w sposób ciągły. Takime systemy może stanowić aparatura medyczna, pod którą podłączani są pacjenci, gdy ich stan wymaga ciągłej kontroli, a decyzja np. o wyłączeniu aparatury jest podejmowana rzadko.

-

Wymagana ciągła kontrola i ciągłe sterowanie - Systemy Czasu Rzeczywistego (z ang. Real Time Computiing [3]). Są to systemy, których wyniki pomiarów mają decydujący wpływ na pracę innych jednostek funkcjonalnych, a decyzję o działaniu (na podstawie wyników pomiarów) należy podjąć w możliwe najkrótszym czasie.Tego typu systemy wykorzystuje się np. w myśliwcach do precyzyjnego sterowania lotem.

Podstawowymi strukturami RSP są:

-

Struktura multiplekserowa, charakteryzująca się topologią gwiazdy, gdzie wymiana informacji przekazywana jest jednokierunkowo,

-

Struktura sieciowa, charakteryzującą się topologią magistralową, gdzie komunikacja zachodzi dwukierunkowo.

Rozproszonym systemem pomiarowym typu sieciowego jest Modularny System Fotoniczny (MSF [4]) opracowany w laboratorium PERG/ELHEP.

1.2. Modularny System Fotoniczny

Celem opracowania MSF było zespolenie różnych czujników fotonicznych w węzłach. Zadaniami MSF są m. in.:

-

Sterowanie procesami pomiarowymi z poziomu sprzętowego i programistycznego,

-

Zautomatyzowane przetwarzanie i akwizycja danych,

-

Ciągła kontrola i diagnozowanie w celu utrzymania jakości pomiarów.

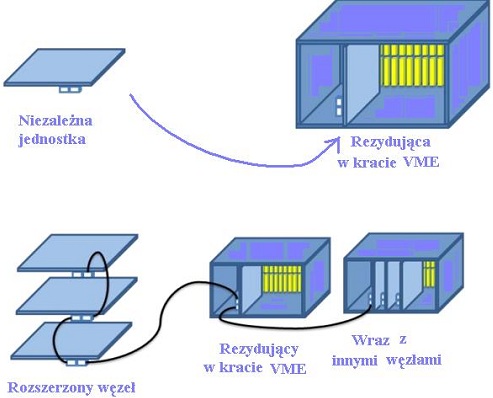

Węzły mogą pracować w konfiguracjach pojedynczej jednostki lub jako element struktury rozproszonej. Na rys. 1.1 przedstawiono powyżej opisane konfiguracje.

Rysunek 1.1. MSF - konfiguracje [5] (VME - Versa Module European [6], krata VME [7])

W ramach prac badawczo-rozwojowych w laboratorium PERG został opracowany węzeł systemu MSF oraz jednostki funkcjonalne rozszerzające jego możliwości. Wspólnie tworząc, tzw. Pełny Węzeł Modularnego Systemu Fotonicznego (PWMSF).

1.3. Pełny Węzeł Modularnego Systemu Fotonicznego

Podstawowym węzłem MSF jest płyta bazowa o nazwie "Universal Module Controller" (UMC [8]) przedstawiona w rozdziale 1.3.1. W celu rozszerzenia funkcjonalności UMC zostały wykonane 2 karty PMC (PCIMezzanine Card [9]) nazwane "Data Acqusition Card" (DAC [10]) oraz "Digital Interface Card" (DIC [11]), które zostały opisane kolejno w rozdziałach 1.3.2 i 1.3.3. Opis kompletnego PWMSF i środowiska jego pracy został przedstawiony w rozdziale 1.3.4.

1.3.1. Płyta UMC

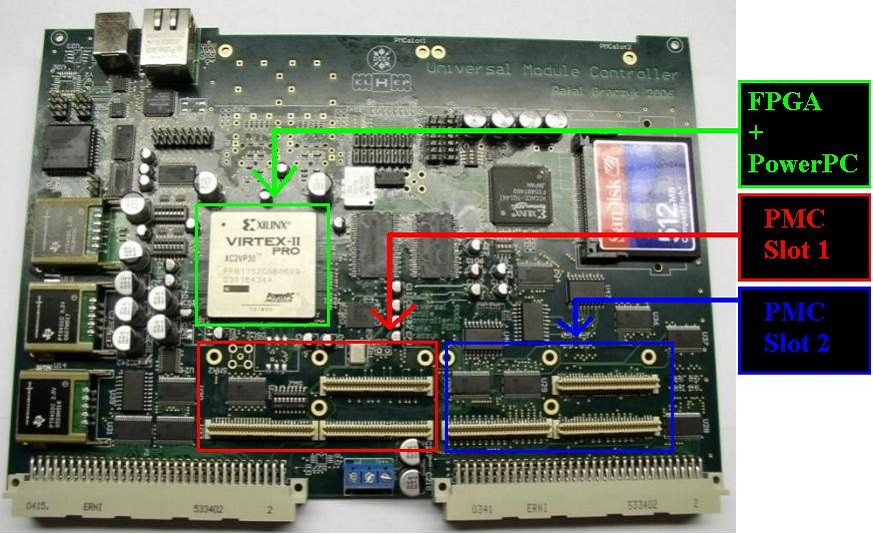

Płyta UMC, prezentowana na rys. 1.2, została wykonana w standardzie mechanicznym EURO-6HE [12] o rozmiarze B (6U - Size B) i jest zgodna elektrycznie ze standardem VME/VXI (VXI - VME eXtensions for Instrumentation [13]).

Rysunek 1.2. Płyta UMC [5]

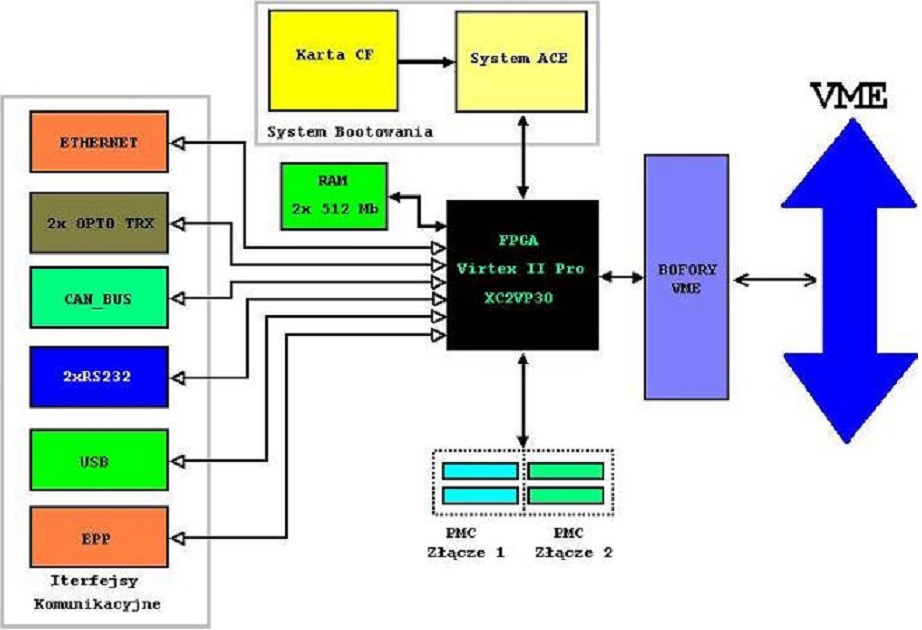

Elementami płyty bazowej UMC są interfejsy komunikacyjne, układ FPGA (Field Programmable Gate Array [14]) mogący pełnić funkcję translacji protokołów (Glue-logic), oraz złącza PMC. Na rys. 1.3 prezentowane są w formie blokowej zasoby płyty.

Rysunek 1.3. Schemat blokowy UMC [15]

UMC wyposażono w Ethernet [16] i gigabitowe łącza światłowodowe. Dodatkowo UMC obsługuje magistrale CAN_BUS (Controler Area Netwoek Bus [17]), RS232 (Recommended Standard 232 [18]), USB (Universal Serial Bus [19] ) oraz port drukarkowy EPP (Enhanced Parallel Port [20]). UMC zawiera system automatycznej konfiguracji uruchamiany po włączeniu zasilania (bootowania). Użytkownik może wybrać odpowiedni tryb konfiguracji:

-

SystemACE (System Advanced Configuration Environment [21]) i karty Compact Flash,

-

EEPROM konfiguracyjny,

-

programator wpięty w łańcuch JTAG (dawniej Joint Test Action Group, - dziś Standard - Test Access Port and Boundary-Scan Architecture[22])

Centralnym elementem UMC jest układ FPGA Virtex II Pro [23](XC2VP30) firmy Xilinx. Układ ten zawiera 30816 komórek LCELL2, 2448 Kb pamięci wbudowanej Block SelectRAM+ [24] o podwójnym dostępie (DUAL-PORT SRAM), 8 układów DCM (Digital Clock Manager [25]), 136 wbudowanych układów mnożących 18x18 bitów, 8 modułów RocketIO [26] pozwalających na bezpośrednią integrację z konwerterami optycznymi, dwa wbudowane 32-bitowe procesory Power-PC 405a klasy RISC (Reduced Instruction Set Computers [27]). Na płycie znajdują się również dwa układy pamięci SD-RAM MT48LC32M16A2 [28] o pojemności 512Mb połączone wspólną szyną adresową w 1024Mb podzielone na 16-bitowe słowa. Całość taktowana jest zegarem 20MHz.

PWMSF posiada również dwa złącza IEEE 1386 Mezzanine Connector umożliwiające rozszerzanie funkcjonalności węzła poprzez dołączanie kart nakładkowych wykonanych w standardzie PMC.

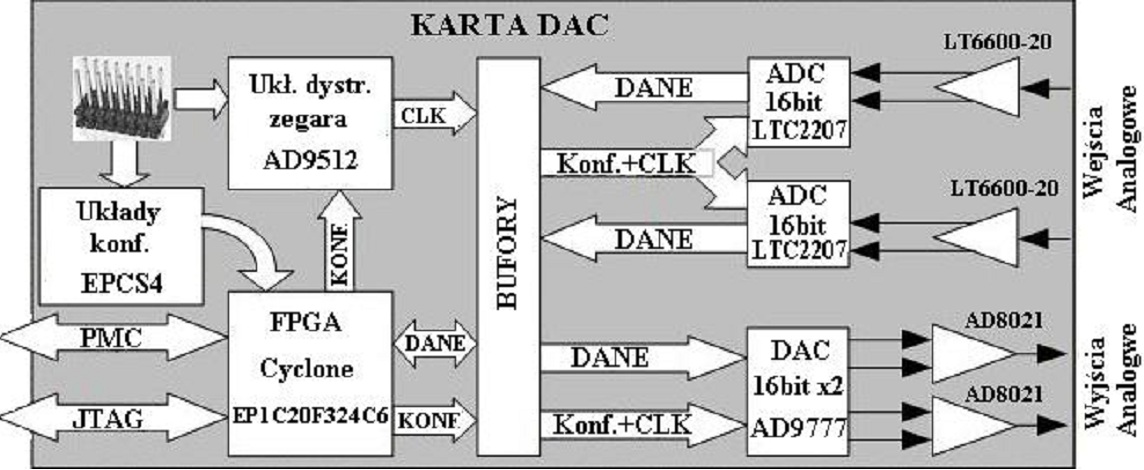

1.3.2. Płyta nakładkowa DAC

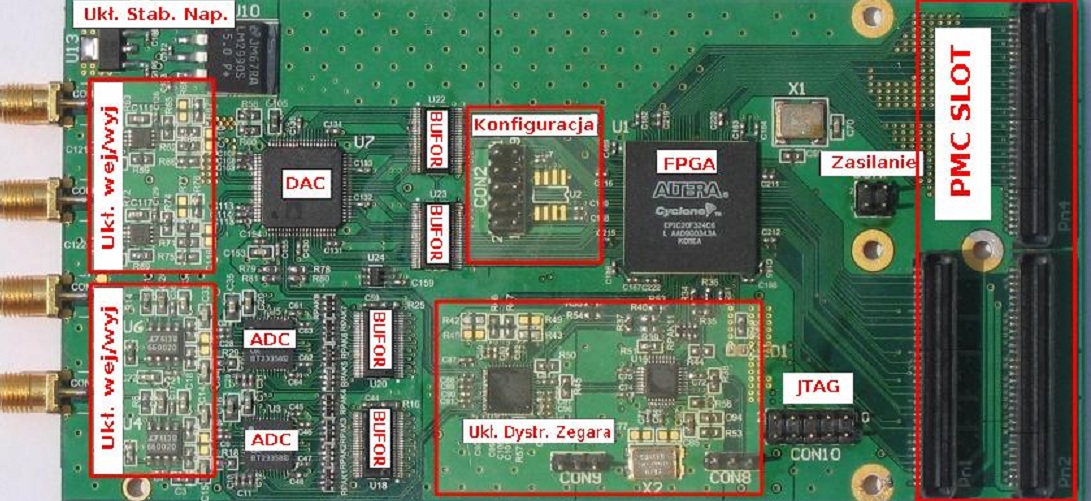

Karta DAC, pokazana na rys. 1.4, została wyposażona przetworniki Analogowo/Cyfrowe (A/C, z ang. Analog-Digital A/D [29]) o maksymalnej częstotliwości próbkowania 100MHz oraz przetworniki Cyfrowo/Analogowe (C/A, z ang. Digital-Analog D/A [29]) generujące sygnały z pasma 0–20MHz.

Rysunek 1.4. Płyta DAC [10]

Elementami płyty nakładkowej DAC, poza przetwornikami A/C oraz C/A, są układ FPGA mogący pełnić funkcję Glue-logic oraz sterowania i konfiguracji przetworników oraz układy dystrybucji zegara oraz złączę PMC. Poniżej na rys. 1.5 prezentowane są ideowo zasoby płyty.

Rysunek 1.5. Schemat blokowy DAC [10]

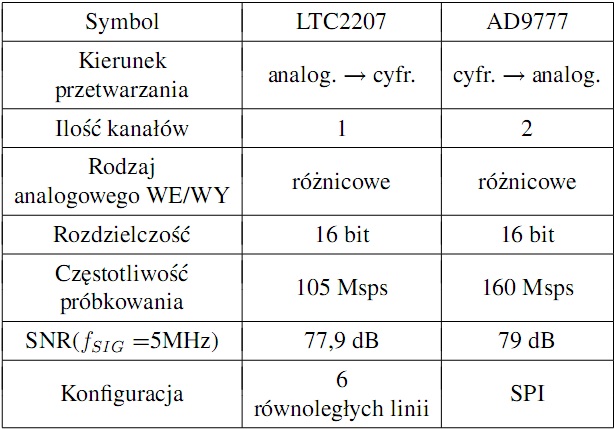

DAC wyposażono w dwa jednokanałowe przetworniki A/C (LTC2207 [30]) oraz jeden dwukanałowy przetwornik C/A (AD9777 [31]). Podstawowe parametry przetworników zestawiono w tabeli 1.1.

Tabela 1.1. Podstawowe parametry przetworników [10]

Przetworniki posiadają następujące opcje konfiguracyjne;

LTC2207 :

-

możliwość pracy w trybie wewnętrznego ditheru,

-

możliwość randomizacji danych wyjściowych za pomocą operacji: out[15..1] = XOR(out[15..1], out[0]),

-

stabilizator współczynnika wypełnienia zegara,

-

wskaźnik przepełnienia zakresu.

AD9777 :

-

filtr interpolujący próbki wyjściowe (obieralny stopień interpolacji: 2x/4x/8x),

-

programowalne wzmocnienie oraz składowa stała dla każdego kanału,

-

wewnętrzny powielacz zegara z pętlą fazową,

-

programowalny wewnętrzny podzielnik zegara.

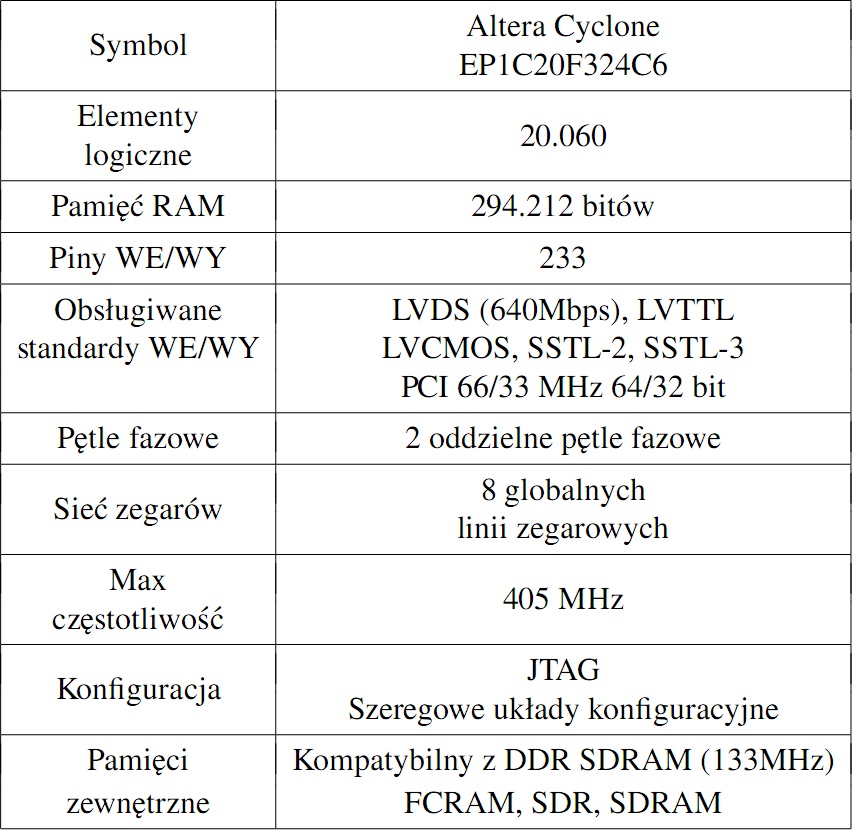

W celu dystrybucji sygnału zegarowego taktującego przetworniki zostały wykorzystane układy AD9512 [32] oraz MAX9452 [33]. Zadaniem AD9512 jest translacja standardu elektrycznego LVDS wejściowego sygnału zegarowego, na standardy obsługiwane przez przetworniki (A/C–LVDS, C/A–LVPECL). Dodatkową możliwością tego układu jest między innymi skonfigurowanie dzielnika częstotliwości dla każdego wyjścia oddzielnie (czyli dla obu kanałów C/A, dla 1 kanału A/C i osobno dla 2 kanału A/C). Zadaniem MAX9452 jest minimalizacja jitteru sygnału zegarowego (pochodzącego z układu FPGA). Wyjściowy sygnał z MAX9452 jest wprowadzany na układ AD9512 w celu translacji standardu elektrycznego i może być doprowadzony do przetworników. Wadą układu MAX9452 jest maksymalna częstotliwość wyjściowa, wynosząca 11MHz ze względu na wykorzystany na płycie DAC oscylator do którego jest podłączony MAX9452. Elementem zespalającym wszystkie układy jest układ FPGA Cyclone (EP1C20F324C6) firmy Altera [34]. Podstawowe parametry układy Cyclone zestawiono w tabeli 1.2. Całość może być taktowana dostępnym na płycie zegarem 100MHz.

Tabela 1.2. Podstawowe parametry Cyclone EP1C20F324C6 [10]

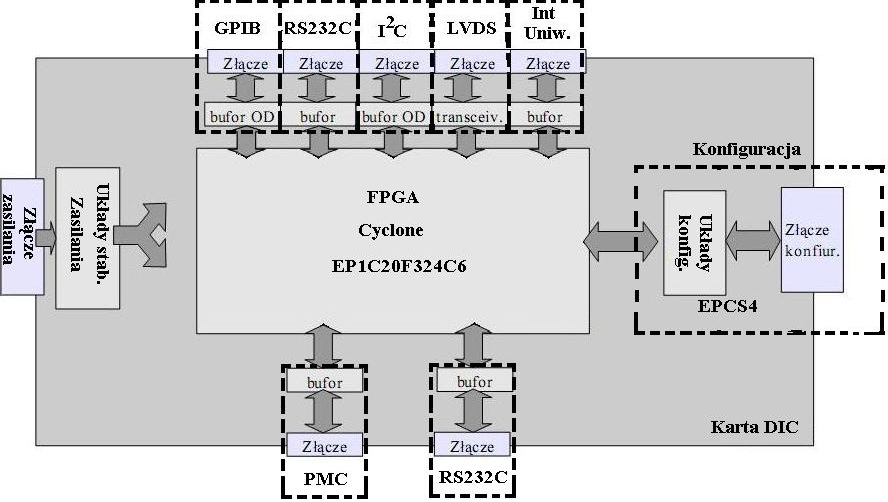

1.3.3. Płyta nakładkowa DIC

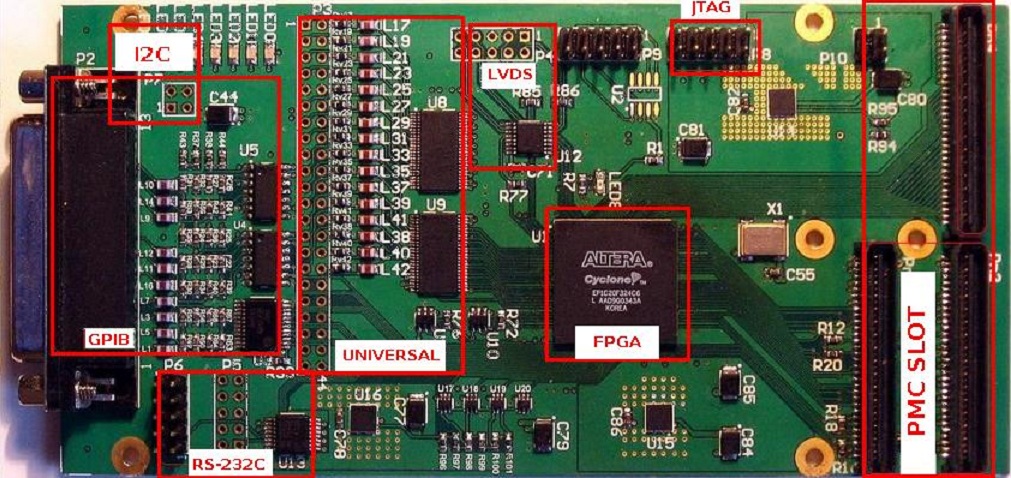

Karta DIC, pokazana na rys. 1.6, rozszerza możliwości węzła o funkcje komunikacji poprzez takie interfejsy jak GPIB (General Purpose Interface Bus [35]), I2C (Inter-Integrated Circuit [36]), JTAG oraz dwa dodatkowe interfejsy RS-232C. Interfejsy te są typowymi interfejsami licznych urządzeń pomiarowych.

Rysunek 1.6. Płyta DIC [11]

Wszystkie interfejsy podłączone są poprzez odpowiednie bufory [11] do układu FPGA Cyclone (EP1C20F324C6) firmy Altera. Poniżej na rys. 1.7 prezentowany jest schemat ideowy płyty DIC i połączeń interesów z układem FPGA.

Rysunek 1.7. Płyta DIC [11]

1.3.4. Konfiguracja sprzętowa PWMSF

PWMSF może być umieszczony w kracie Eurocard (VME), co umożliwia komunikację z innymi płytami w kracie oraz z innymi urządzeniami wykorzystując cały zbiór peryferii z samego PWMSF. Komunikacja z innymi węzłami MSF odbywa się za pośrednictwem łącz optycznych. Dodatkowo PWMSF może zostać dołączony do sieci lokalnej lub internetowej dzięki interfejsowi Ethernet na płycie UMC. Poniżej od góry prezentowane jest połączenie płyt w PWMSF (rys. 1.8) wraz z wyprowadzeniami JTAG oraz włożony węzeł do kraty VME wraz z kluczowymi dla systemu pomiarowego interfejsami.

Rysunek 1.8. PWMSF w kracie VME (na górze). Węzeł w kracie VME (na dole) [5]

---------------------------

-

Wiesław Winiecki. Rozproszone Systemy Kontrolno Pomiarowe – wykład, 2008.

-

Bluetooth SIG. Specification of the Bluetooth System. http://www.bluetooth.com/Bluetooth/ Technology/Building/Specifications/, Listopad 2004.

-

Krzysztof Sacha. Systemy czasu rzeczywistego. Oficyna Wydawnicza Politechniki Warszawskiej, 1999.

-

Artur Dybko, Rafał Graczyk, Krzystof T. Po´zniak, Ryszard S. Romaniuk. Modularny system fotoniczny z programowalną warstwą sterowania i komunikacji w układzie FPGA, 2006.

-

Samer Bou Habib, Ryszard Romaniuk. Opracowanie Mostu PCI dla Węzła Modularnego Systemu Fotonicznego. Politechnika Warszawska, 2008.

-

Wade D. Peterson. The VMEbus Handbook 2nd edition. VITA.

-

WIENER. Series 6000 VME, -64x, -64xC, -64xP, VXI User’sManual. http://www.wiener-d/com/documents/contentdocuments/7.pdf.

-

Rafał Graczyk, Krzysztof T. Poźniak, Ryszard S. Romaniuk. FPGA based, modular, configurable controller with fast synchronous optical network. Proc of SPIE vol. 6347 part one, 2006.

-

IEEE Standard Physical and Environmental Layers for PCI Mezzanine Cards (PMC). ieeexplore.ieee.org/iel5/7509/20428/00944007.pdf, 2001.

-

Łukasz Dymanowski. Projekt i wykonanie modułu akwizycji danych z wykorzystaniem standardu PMC. Politechnika Warszawska, 2007.

-

Kamil Lewandowski. Projekt i wykonanie karty PMC z interfejsami komunikacyjnymi. Politechnika Warszawska, 2007.

-

VMEbus Card Form Factors. http://www.interfacebus.com/Design_VME_Card_size.html.

-

VME eXtensions for Instrumentation. http://www.vxibus.org/.

-

PartMiner, Inc. FPGA (FIELD-PROGRAMMABLE GATE ARRAY). http://www.partminer.com/glossaryhtml/fpga_field_programmable_gate_array..., 2005.

-

Rafał Graczyk, Krzystof T. Poźniak. Projekt i uruchomienie uniwersalnego kontrolera szyny VME: ”Universal Module Controller”. Praca magisterska, Politechnika Warszawska, 2009.

-

IEEE. IEEE Standard for Information technology-Telecommunications and information exchange between systems-Local and metropolitan area networks-Specific requirements. http://standards.ieee.org/getieee802/802.3.html, 2008.

-

BOSCH. CAN Specification Version 2.0. www.semiconductors.bosch.de/pdf/can2spec.pdf, Czerwiec 1991.

-

Peter L. B. Johnson. Summer 2004 Laboratory Notes: Computer Engineering II. http://courses.ece.illinois.edu/ece390/books/labmanual/serial-comm-standards.html.

-

USB Implementers Forum, Inc. Universal Serial Bus Revision 2.0 specification. http://www.usb.org/developers/docs/usb_20_122909-2.zip.

-

Clark L. Buxton, Robert A. Kohtz. Enhanced Parallel Port, US Patent number: 5636348. http://v3.espacenet.com/textdocfiDB=EPODOC&IDX=EP0640229.

-

Xilnix. System ACE. http://www.xilinx.com/support/documentation/system_ace_solutions. htm.

-

Texas Instruments. IEEE Std 1149.1 (JTAG) Testability. http://focus.ti.com/lit/an/ssya002c/ssya002c.pdf, 1997.

-

Xilinx. Xilinx virtex ii pro platform fpga : Complete data sheet. www.xilinx.com/support/documentation/data_sheets/ds083.pdf, 2007.

-

Xilnix. Block SelectRAM+. http://www.nalanda.nitc.ac.in/industry/appnotes/xilinx/documents/products/xaw/memory/embedded/blockram.htm.

-

Xilnix. Digital Clock Manger. http://www.xilinx.com/itp/xilinx7/books/data/docs/s3edl/s3edl0021_13.html.

-

Xilinx. RocketIOTM Transceiver User Guide. www.ee.ucla.edu/~herwin/ocdma/afx-300/ug024.pdf.

-

Jan Ogrodzki. Wst˛ep do systemów komputerowych, rozdział 8. Oficyna Wydawnicza Politechniki Warszawskiej, 2005.

-

MICRON. MT48LC32M16A2 - Synchronous DRAM . http://www.datasheetcatalog.com/datasheets_pdf/M/T/4/8/MT48LC32M16A2.shtml.

-

Walt Kester. Analog-Digital Conversion. Analog Devices, Inc., 2004.

-

Linear Technology. LTC2207/LTC2206 Datasheet. http://www.linear.com/pc/downloadDocument.dofinavId=H0,C1,C1155,C1001,C1150,P13913,D9837.

-

Analog Devices. AD9777 Datasheet Rev Ct. http://www.analog.com/UploadedFiles/Data_Sheets/AD9777.pdf, Styczeń 2006.

-

Analog Devices. AD9512 Datasheet. http://www.analog.com/UploadedFiles/Data_Sheets/AD9512.pdf, Czerwiec 2005.

-

Maxim. MAX9450-MAX9452 Datasheet. http://datasheets.maxim-ic.com/en/ds/MAX9450-MAX9452.pdf.

-

Altera. Cyclone Device Handbook. http://www.altera.com/literature/hb/cyc/cyc_c5v1.pdf, 2006.

-

The Institute of Electrical and Electronic Engineers. GPIB : ANSI/IEEE Std 488.1-1987, IEEE Standard Digital Interface for Programmable Instrumetation, New York 1988.

-

Philips. THE I2C-BUS SPECIFICATION Version 2.1. http://www.nxp.com/acrobat/literature/9398/39340011.pdf, Styczeń 2000.